Hallo zur Webseite von

DL1DMW

DL1DMW

So funktioniert's:

Das I2C-Protokoll

Features:

- I2C-Start und Stop

- I2C-Arbitration

- I2C Data Frame

- I2C Lesen

- I2C Schreiben

Es gibt serielle Kommunikationsprotokolle wie z. B. SPI, UART, I2C und andere, die zur Kommunikation von Chips (IC) und Komponenten bzw. Baugruppenm untereinander zur Verfügung stehen.

I2C ist die Kurzform von Inter-Integrated-Circuit (IIC oder I2C). Es ist ein Bus, der 1980 von Philips für die Inter-Chip-Kommunikation entwickelt wurde und von vielen Herstellern für die Chip-to-Chip-Kommunikation übernommen wurde (andere Chip-Hersteller als Philips sprechen aus Gründen des Copyrights von TWI (twin wire interface)). Mit I2C kommunizieren zwei IC (innerhalb eines Gerätes) miteinander. I2C spart gegenüber parallelen Interfaces (z. B. einem Parallelbus für 8 Bits) einige Leitungen des µControllers ein und damit Platz auf der Platine. Der Vorteil vervielfältigt sich, sobald mehrere IC mit einem Bus verbunden sind.

Das I2C ist ein serielles Multi-Master und Multi-Slave Kommunikationsprotokoll, das bedeutet, dass wir die Möglichkeit haben, mehrere ICs gleichzeitig am selben Bus anzuschließen. Im I2C-Protokoll wird die Kommunikation immer vom Master gestartet und bei Multi-Master übernimmt jeweils nur ein Master den Bus.

Was ist I2C?

I2C bietet eine gute Unterstützung langsamer Geräte wie z. B. EEPROM, ADC (Analog-Digital-Wandler), RTC (Real Time Clock, Echtzeituhr), Port-Expander, LCD und vieles mehr. I2C wird nicht nur innerhalb der Grenzen einer Platine verwendet, sondern darüber hinaus auch bei anderen externen Komponenten (Baugruppen) eines Gerätes, die über Kabel mit der Platine verbunden sind.

I2C ist ein Zweileiter-Kommunikationsprotokoll, das zwei Drähte zur Kommunikation verwendet. Zur Übertragung der Daten wird ein Signal (SDA) benötigt, ein weiteres überträgt das Taktsignal (SCL).

In I2C sind beide Busleitingen bidirektional, d. h. der Master kann die Daten zum Slave senden und von dort empfangen. Der Takt wird vom Master gesteuert, aber in einigen wenigen Situationen kann der Slave auch das Taktsignal unterdrücken / verzögern, dazu später mehr.

Neben den genannten Anwendungen wird der I2c-Bus in verschiedenen Steuerungsarchitekturen eingesetzt, wie z. B. SMBus (System Management Bus), PMBus (Power Management Bus), IPMI (Intelligent Platform Management Interface) etc.

Warum I2C?

Im Gegensatz zur seriellen Schnittstelle (RS232) nutzt I2C die synchrone Kommunikation, bei der sowohl Master als auch Slave den vom Master erzeugten Shared Clock verwenden.

Bei einer seriellen Schnittstelle (RS232) haben bei Sender und Empfänger jeweils einen eigenen Taktgenerator. Dort ist es sehr wichtig, eine mögliche Differenz zwischen dem Takt des Senders und des Slaves zu minimieren, da sonst die Daten während der Kommunikation beschädigt werden.

Ein weiterer Nachteil des asynchronen seriellen Com-Ports ist, dass nur zwei Geräte die Daten senden und empfangen können, im Gegensatz dazu kann I2C auch als Multi-Master (mehrere Master an einem Bus) und Multi-Slave (mehrere Slave an einem Bus) ausgeführt werden. RS232 nutzt ein UART-Chip für die Kommunikation. Für die asynchrone Kommunikation ist kein spezifischer Grenzwert definiert, die meisten seriellen Geräte unterstützen eine maximale Baudrate von 230400 Bits pro Sekunde.

SPI dagegen arbeitet Vollduplex und ist schneller als I2C, obwohl I2C manchmal viel einfacher und vorteilhafter ist. Bei I2C nutzen wir zwei Drähte für die Kommunikation, bei SPI sind es derer vier Drähte! I2c kann Multi-Master sein, aber SPI kann niemals Multi-Master sein. Mehrere Datenempfänger sind aber auch bei SPI möglich.

Eigenschaft des I2C-Bus

- In I2C werden für die Kommunikation nur zwei Leitungen benötigt, die serielle Datenleitung (SDA) und der serielle Takt (SCL).

- Jede Komponente im I2C-Bus ist per Software adressierbar mit einer eindeutigen Adresse, diese Adresse wird vom Master zur Kommunikation mit einem bestimmten Slave verwendet.

- In I2C gibt es immer eine Master- und Slave-Beziehung.

- In I2C wird die Kommunikation immer vom Master gestartet.

- Der I2C-Bus bietet die Möglichkeit der Arbitrierung und Kollisionserkennung.

I2C ist die auf 8-Bit orientierte serielle bidirektionale Kommunikation, es gibt folgenden Geschwindigkeitsmodus in I2C

I2C - die physikalische Schicht

I2C ist ein reines Master- und Slave-Kommunikationsprotokoll, es kann Multi-Master oder Multi-Slave sein, aber wir sehen in der Regel einen einzelnen Master (z. B. einen Mikrocontroller) in der I2C-Kommunikation. Bei I2C werden nur zwei Drähte für die Kommunikation verwendet, eine davon ist der Datenbus (SDA) und die zweite ist der Taktbus (CLK).

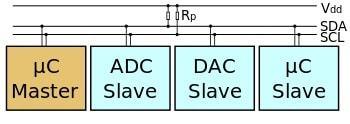

<- Bild2: I2C-Bus mit einem Master und drei Slaves.

Alle Slave und Master sind mit dem gleichen Daten- und Taktbus verbunden, wichtig ist hierbei zu beachten, dass diese Busse über die WIRE-AND-Konfiguration miteinander verbunden sind (Open Drain).

Open Drain ermöglicht es dem Master und Slave, die Leitung niederohmig zu treiben und in den hochohmigen Zustand zu versetzen. In dieser Situation, wenn Master und Slave den Bus freigeben, benötigen Sie also einen Pull-Up-Widerstand, um die Leitung hochzuziehen. Der Wert des Pull-Up-Widerstandes ist sehr wichtig, da ein falsche Wert zu ungewollten Signalverlusten führen kann.

Hinweis: Wir wissen, dass das I2c-Kommunikationsprotokoll die verschiedenen Master und mehrere Slaves unterstützt, aber die meisten Systemdesigns enthalten nur einen Master - meist einen Mikrocontrroller, der den Bus im Gerät steuert.

Das I2C-Protokoll

I2C ist das einfachste Chip-to-Chip Kommunikationsprotokoll. Wenn der Master mit dem Slave kommunizieren will, dann setzt er ein Startbit, gefolgt von der Slaveadresse mit Lese-/Schreibbit.

Nach dem Absetzen des Startbits befindet sich alle Slaves im Achtsamkeitsmodus. Wenn die gesendete Adresse mit der Adresse eines der Slaves übereinstimmt, wird vom Slave ein ACKNOWLEDGEMENT Bit (ACK) an den Master gesendet.

Nach dem Empfang des ACK-Bits startet der Masters die Kommunikation. Wenn kein Slave vorhanden ist, dessen Adresse mit der gesendeten Adresse übereinstimmt, dann hat der Master ein NOT-ACKNOWLEDGEMENT (NACK) Bit empfangen, in diesem Fall wird der Master entweder das Stoppbit auf die Leitung legen, um die Kommunikation zu stoppen oder aber ein wiederholtes Startbit (Repeated Start) auf der Leitung geben, um eine neue Kommunikation zu beginnen.

Das Data Frame

I2C ist ein 8-Bit Kommunikationsprotokoll, bei I2C erhalten wir nach jedem Byte ACK (Acknowledgment) oder NACK (Not Acknowledgment) Bits. Hier einige wichtige Begriffe, die sich auf den I2c Datenrahmen (Frame) beziehen:

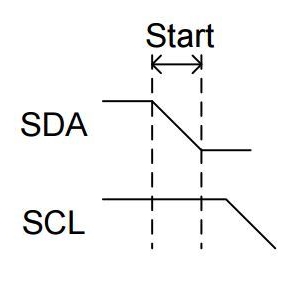

Start

Der Standardzustand der SDA- und SCL-Leitung ist ein High-Pegel. Ein Master tätigt die Startbedingung auf der Leitung, um die Kommunikation zu starten. Ein High-zu-Low-Übergang der SDA-Leitung, während die SCL-Leitung weiterhin High bleibt, gilt als START-Bedingung. START wird immer vom Master ausgeführt. Der I2C-Bus gilt nach dem Absetzen des START-Bits als vom Master besetzt.

<- Bild 3: Start

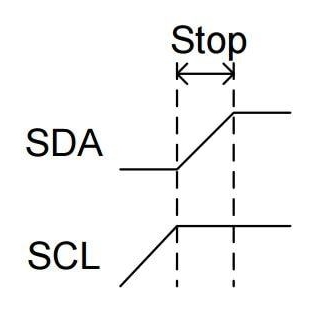

Stopp

Die STOP-Bedingung wird vom Master getätigt, um die Kommunikation zu stoppen. Ein Low-zu-High-Übergang der SDA-Leitung, während die SCL-Leitung auf High bleibt, gilt als STOP-Zustand. Der STOP-Zustand wird immer vom Master getätigt. Der I2C-Bus gilt nach dem Stop-Bit als frei. Es könnte nun derselbe oder ein anderer Master mit einem Start-Bit den Bus belegen.

<- Bild 4: Stop

Hinweis: START und STOP werden immer vom Master ausgeführt.

Repeated Start

Der wiederholte Start ist ähnlich der START-Bedingung, aber beide unterscheiden sich voneinander. Wiederholter Start wird vom Master vor dem Stop-Zustand (Wenn sich der Bus nicht im Ruhezustand befindet) getätigt.

Ein Wiederholter Startzustand wird vom Master ausgeführt, wenn er die Kontrolle über den Bus nicht verlieren will. Ein wiederholter Start ist für den Master vorteilhaft, wenn er eine neue Kommunikation starten will, ohne zuvor Stop zu geben.

Hinweis: Ein wiederholter Start ist vorteilhaft, wenn mehr als ein Master am I2c-Bus angeschlossen ist und der aktuelle Master den Bus nicht freigeben möchte.

Das Byte-Format

In I2C müssen alle Daten, die über die SDA-Leitung übertragen werden, acht Bit lang sein. Es ist sehr wichtig zu wissen, dass das von einem Byte zuerst das MSB übertragen wird und dass wir zwischen einem Start- und Stopp-Zustand eine beliebige Anzahl von Bytes senden oder empfangen können.

Bild 5: Datentransfer

Wenn wir die Bytes in I2C senden oder empfangen, erhalten wir immer ein ACK-Bit oder NACK-Bit, nachdem jedes Byte der Daten während der Kommunikation übertragen wurde.

In I2C wird bei jedem Taktzyklus immer ein Datenbit übertragen. Ein Byte, das in I2C übertragen wird, kann z. B. eine Adresse eines IC des Gerätes, die Adresse eines Registers oder Daten sein, die in den Slave geschrieben oder vom Slave gelesen werden.

Grundsatz: In I2C ist die SDA-Leitung während der Hochtaktphase (SCL ist High) immer stabil, mit Ausnahme der Startbedingung, der Stop-Bedingung und der wiederholten Startbedingung (repeated Start). Die SDA-Leitung wechselt ihren Zustand nur während der Low-Clock-Phase (SCL ist Low).

Merke: SDA kann den Zustand nur verändern, in dem SCL Low wird, Ausnahmen sind die Start-, Repeated-Start und Stop-Bedingung.

Handshake-Verfahren im I2C-Protokoll

In I2C muss für jedes Byte ein Acknowledgment vom Empfänger gesendet werden, dieses Acknowledgment-Bit (ACK) ist ein Beweis dafür, dass die Daten vom Empfänger korrekt empfangen werden und er die Kommunikation fortsetzen will.

Ein Master startet die Kommunikation und legt eine Startbedingung auf den Bus. Nach der Übertragung des Startbits wird eine 7-Bit-Adresse mit zugehörigen Lese- oder Schreibbits übertragen.

Nach dem Senden des Adressbytes gibt der Master die Datenleitungen frei und versetzt die Datenleitung (SDA) in den hochohmigen Zustand, wodurch der Empfänger die Quittierung erteilen kann.

Wird diese gesendete Adresse mit einem beliebigen Empfänger erfolgreich abgeglichen, so wird die SDA-Leitung für die Quittierung auf Low-Pegel gelegt und nach der Quittierung die Datenleitung freigegeben. Der Master erzeugt einen Taktimpuls, um dieses Quittungsbit zu lesen und den Lese- oder Schreibbetrieb fortzusetzen.

Wird diese gesendete Adresse nicht mit einem Empfänger abgeglichen (kein passender Slave vorhanden), dann zieht also niemand die Datenleitungen auf Low, der Master versteht, dass es sich um einen NACK handelt und in diesem Fall wird der Master ein Stoppbit sendet oder ein wiederholtes Startbit (reperated Start) senden.

Quittieren (ACK) und Nicht Quittieren (NACK)

In den obigen Zeilen wurden die Bits ACK (Acknowledgment) und NACK (Not Acknowledgement) und ihre Bedeutung im I2C-Protokoll beschrieben. Im folgenden ein Szenario, bei dem ein NACK-Bit erzeugt wird.

Wenn der Empfänger die Daten nicht empfangen oder senden kann, erzeugt er in dieser Situation ein NACK-Bit, um die Kommunikation zu stoppen.

Erhält der Empfänger während der Kommunikation Daten oder Kommandos, die vom Empfänger nicht verstanden werden, generiert er ein NACK-Bit.

Wenn der Empfänger während der Übertragung einen Echtzeitbetrieb durchführt und nicht mit dem Master kommunizieren kann, dann setzen Sie ein NACK-Bit.

Wenn der Master ein Empfänger ist und die Daten vom Slave liest, dann setzt er nach dem Auslesen der gesamten Daten ein NACK-Bit auf die Datenleitungen, um die Kommunikation zu stoppen.

Befindet sich kein Gerät auf dem I2C-Bus mit der gleichen Adresse, die vom Master übertragen wird, so erhält der Master von keinem Slave die Quittierung und behandelt diese Situation als NACK.

I2C-Schreibvorgang

In I2c muss bei Schreiboperationen der Master vor dem Schreiben eines Datenbytes zuerst eine Startbedingung auf den I2C-Bus legen, dann die Adresse des Slaves mit dem Schreibkontrollbit. Beim Schreibvorgang ist das Kontrollbit jeweils 0.

Wenn die gesendete Adresse mit einem beliebigen Slave, der am I2C-Bus angeschlossen ist, übereinstimmt, erhält der Master ein Acknowledge-Bit. Nachdem der ACK-Bit-Master die Adresse des Registers, in das er schreiben möchte, erhalten hat, quittiert der Slave erneut und teilt dem Master mit, dass er für den Schreibvorgang bereit ist.

Bild 6: Schreiboperation, Slave quittiert korrekten Empfang mit ACK.

Nach Erhalt dieser Quittierung beginnt der Master, die Daten an den Slave zu senden. Der Master erhält die Quittierung jedes übertragenen Datenbytes.

Erhält der Master vom Slave die Quittierung nicht, dann setzt der Master eine Stop-Bedingung, um die Kommunikation zu stoppen oder aber den wiederholten Start zum Aufbau einer neuen Kommunikation.

Es gibt noch eine andere Möglichkeit, die Kommunikation zu stoppen, nachdem der Master alle Daten gesendet hat.

I2C Lesevorgang

Die I2C-Leseoperation ist ähnlich wie die I2C-Schreiboperation, auch hier beginnt der Master mit der Startbedingung. Nach der Startbedingung legt der Master die Slaveadresse mit dem Lesenkontrollbit (beim Lesebetrieb ist das Kontrollbit jeweils 1) auf den Bus. Wenn die gesendete Adresse mit einem beliebigen IC am I2c-Bus übereinstimmt, quittiert der Slave mit einem Low-Pegel auf der Datenleitung (SDA). das ist dann ein ACK-Bit.

Bild 7: Leseoperation.

Nach dem Erhalt des ACK-Bits, gibt der Master den Datenbus frei, sendet aber den Takt weiter. In diesem Fall wird der Master zum Empfänger und der Slave zum Sender.

Im Lesebetrieb gibt der Master dem Slave beim Empfang jedes Datenbytes die Quittierung an den Slave, um ihn wissen zu lassen, dass er bereit für weitere Daten ist, nachdem der Master die Anzahl der erwarteten Bytes empfangen hat, sendet er ein NACK-Bit, um den Bus freizugeben und danach das Stopbit, um die Kommunikation anzuhalten.

Einige Sonderfälle in I2C

Taktsynchronisierung in I2C

Im Gegensatz zu Rs232 ist I2C eine synchrone Kommunikation, bei der der Master immer einen Takt erzeugt und dieser Takt von Master und Slave gemeinsam genutzt wird.

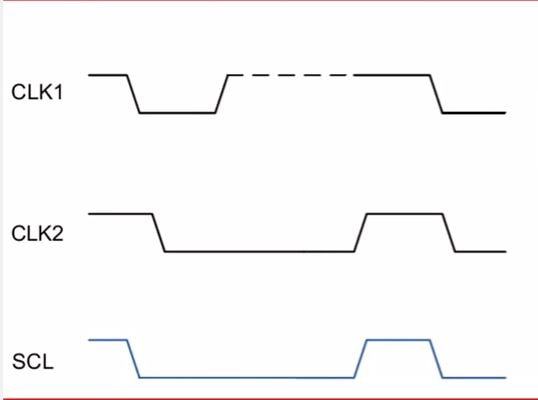

Im Falle von Multi-Master erzeugen alle Master ihren eigenen SCL-Takt, daher ist es notwendig, dass der Takt aller Master synchronisiert wird. Im I2C erfolgt diese Taktsynchronisation über Kabel und Logik.

Zum besseren Verständnis ein Beispiel, wo zwei Master versuchen, mit einem Slave zu kommunizieren. In dieser Situation erzeugen beide Master ihren eigenen Takt, Master M1 erzeugt CLK1 und Master M2 generiert CLK2 und der von alles Slaves "gesehene" Takt ist SCL.

<- Bild 8: Taktsynchronisation zweier Master, die auf den Bus zugreifen.

Das Signal SCL ist die logische UND-Funktion von CLK1 und CLK2. Interessant ist, dass sich hier der Low-Pegel durchsetzt, auch wenn ein Master sein Clock-Signal auf High zieht.

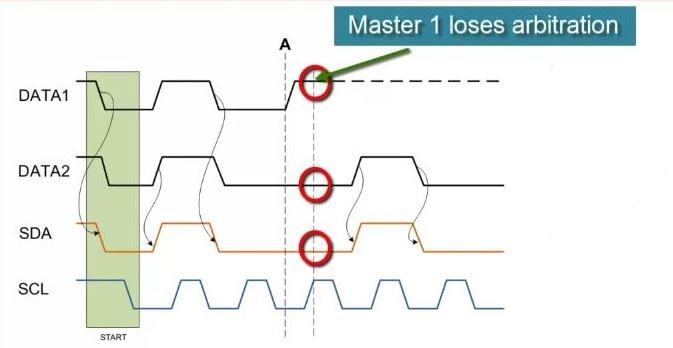

Arbitrierung in I2C

Die Arbitrierung (Regelung für den Zugriff auf den Bus) ist bei Multi-Master erforderlich, wenn mehr als ein Master versucht, gleichzeitig mit einem Slave zu kommunizieren. Bei der I2C-Arbitrierung kommt SDA eine besondere Bedeutung zu.

Angenommen, zwei Master im I2C-Bus versuchen gleichzeitig mit einem Slave zu kommunizieren, dann werden sie eine Startbedingung auf dem Bus legen. Weiter angenommen, der Takt (SCL) des I2C Busses ist durch die Verdrahtung und Logik synchronisiert.

Bild 9: Arbitrierung - Zugriff auf den Bus.

DATA1 stammt von Master 1, DATA2 von Master2, SDA ist die logische Addition von DATA1 und DATA2, also das aus DATA1 und 2 resultierende Signal: In obiger Abbildung ist alles gut, solange der Zustand der SDA-Leitung mit dem übereinstimmt, was die beiden Master auf den Bus legen. Sobald ein Master feststellt, dass sich der Zustand der SDA-Leitung von seinen Daten unterscheidet, verlieren er den Zugriff auf den Bus. Kurz: Wer zuerst die Leitung auf High legen will, verliert den Bus.

Hinweis: Der Master, der seinen Zugriff auf den I2C-Bus verliert, wartet, bis der Bus wieder frei wird.

Clock-Stretching in I2C

In I2c kann die Kommunikation durch die Taktausdehnung auf Low angehalten werden und kann nicht fortgesetzt werden, bis die SCL-Leitung wieder High freigibt.

Bild 10: Slave zieht SCL auf Low und verschafft sich zur Datenverarbeitung mehr Zeit.

Der Slave ist in der Lage, ein Byte mit hoher Geschwindigkeit zu empfangen. Doch manchmal benötigt ein Slave mehr Zeit zur Verarbeitung der empfangenen Bytes. In dieser Situation zieht der Slave das SCL-Signal auf Low, um weitere Transaktionen zu verzögern. Nach der Verarbeitung empfangener Bytes gibt er SCL wieder frei, zieht SCL auf High-Pegel, damit die Kommunikation fortgesetzt werden kann.

Im I2C-Kommunikationsprotokoll verwenden die meisten I2C-Slave-Geräte nicht die Funktion Clock-Stretching, doch jeder Master sollte das Clock-Stretching unterstützen.

Vorteile von I2C

Es gibt viele Vorteile des I2C-Protokolls:

- Es ist das synchrone Kommunikationsprotokoll, dass keine präzisen Oszillatoren für Master und Slave benötigt.

- Es benötigt nur zwei Drähte, ein Kabel für die Daten (SDA) und ein anderes Kabel für den Takt (SCL).

- Es bietet dem Benutzer die Flexibilität, die Übertragungsrate gemäß den Anforderungen zu wählen.

- Im I2C-Bus ist jedes Gerät auf dem Bus unabhängig adressierbar.

- I2C folgt dem Master- und Slave-Prinzip.

- Es hat die Fähigkeit, mehrere Master und mehrere Slaves auf dem I2C-Bus zu verwalten.

- I2C hat einige wichtige Features wie Arbitrierung, Taktsynchronisation und Clock-Stretching.

- I2C bietet ACK/NACK (acknowledgment/ Not-acknowledgement) Funktionen, die bei der Fehlerbehandlung helfen.

Einige wichtige Einschränkungen des I2C-Kommunikationsprotokolls

Ein I2C-Protokoll hat viele Vorteile, aber es gibt auch einige Einschränkungen:

- Aufgrund der offenen Topologie verbraucht I2C mehr Strom als vergleichbare serielle Busse.

- Es ist nur für die kurze Strecke gut (ca 30 cm Buslänge).

- Das I2C-Protokoll hat eine gewisse Begrenzung für die Anzahl der Slaves, die Anzahl der Slaves hängt von der Kapazität des I2C-Bus ab.

- Es verfügt nur über begrenzte Kommunikationsgeschwindigkeiten wie 100 kbit/s, 400 kbit/s etc.

- Bei I2C können IC ihre Kommunikationsgeschwindigkeit einstellen, langsamere IC verzögern den Betrieb schnellerer IC-Bausteine.

Bild 11: I2C (IIC) auch TWI genannt.

Sie möchten das Datenblatt zum I2C-Protokoll im Original lesen? Sie finden die PDF-Datei im Internet.

Schlussfolgerung

I2c ist das einfache und preiswerte Kommunikationsprotokoll, es kommt mit Multi-Master und Multi-Slave zurecht. Bei I2C erhalten Sie nach jedem übertragenen Byte die ACK/NACK-Bits. I2C ist eine Halbduplex-Kommunikation und im Vergleich zu SPI recht langsam, dennoch zuverlässig.

Mehr Zeugs

- Schaun mer mal

- Moin

- Bast scho

Hier gibt es was zu lesen

- dl1dmw.darc.de

- dl1dmw.wordpress.com

- qsl.net/dg5dbz

Adresse etc.

- Op: Michael, DL1DMW

- ITU Region 1, Zone 14, DL, JO41CO

- Bad Sassendorf

- NRW / Germany